JEDEC НгНќЭъГЩ SPHBM4 ЙцЗЖЃКI/O в§НХЪ§СПНігаБъзМ HBM4 ФкДцЕФ 1/4

РДдДЃКithome 2025-12-12 10:56:43xiayx 12 дТ 12 ШеЯћЯЂЃЌJEDEC ЙЬЬЌММЪѕаЛсУРЙњМгжнЕБЕиЪБМф 11 ШеаћВМЃЌЦфвбНгНќЭъГЩ SPHBM4 ФкДцЙцЗЖЁЃетРяЕФ "SP" ЪЧ "Standard Package"ЃЈБъзМЗтзАЃЉЕФЪззжФИМђаДЁЃ

ГЄЦкЮШЖЈИќаТЕФдмОЂзЪдДЃК >>>ЕуДЫСЂМДВщПД<<<

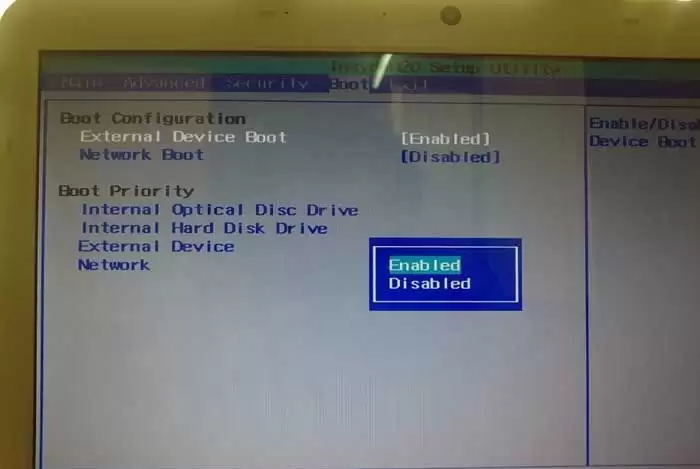

SPHBM4 ЪЙгУгыБъзМ HBM4 ЯрЭЌЕФ DRAM КЫаФВуЃЌСНепдкШнСПРЉеЙЩЯУЛгаВювьЁЃЧјБ№дкгкЃЌSPHBM4 дкНгПкЛљДЁТуЦЌ (Interface Base Die) ВПЗжВЩгУСЫВЛЭЌЕФЩшМЦЃЌПЩАВзАдкБъзМгаЛњЛљАхЖјВЛЪЧЙшЛљАхЩЯЁЃ

ДЫЭтЃЌБъзМ HBM4 ФкДцгЕга 2048 Иі I/O Ъ§Онв§НХЃЌЖјдк SPHBM4 ЩЯетвЛЪ§СПНЋНЕЕЭЕН 512 ИіЁЃЮЊЪЕЯжЯрЕБЕФзмЪ§ОнДЋЪфЫйТЪЃЌSPHBM4 НЋОпгаИќИпЕФЙЄзїЦЕТЪВЂВЩгУ 4:1 ДЎааЛЏММЪѕЁЃетвВЪЧЮЊСЫХфКЯгаЛњЛљАхжЇГжЕФЭЙЕуМфОрУмЖШИќЕЭЕФВФСЯЬиадЁЃ

SPHBM4 ЪЙгУгаЛњЛљАхВМЯпЕФвЛДѓКУДІЪЧдк SoC КЭ HBM ФкДцЖбеЛМфдЪаэИќГЄЕФЯпОЖЃЌетгаРћгкЬсЩ§ЕЅвЛЗтзАжаМЏГЩЕФЖбеЛЪ§СПЃЌДгЖјНјвЛВНЬсИпЯЕЭГФкДцзмШнСПЁЃ

ЯРгЮЯЗЗЂВМДЫЮФНіЮЊСЫДЋЕнаХЯЂЃЌВЛДњБэЯРгЮЯЗЭјеОШЯЭЌЦфЙлЕуЛђжЄЪЕЦфУшЪі

ЯрЙиЙЅТд

ИќЖрЭЌРрИќаТ

ИќЖрШШгЮЭЦМі

ИќЖр-

- КНЬьЛ№М§ФЃФтЦї

- Android/ | ФЃФтбјГЩ

- 2026-04-07

-

- УќдЫЦяЪПЭХ

- Android/ | НЧЩЋАчбн

- 2026-03-30

-

-

-

-

-

- зЙаЧДѓТН ТђЖЯАц

- Android/ | НЧЩЋАчбн

- 2026-03-30

-

- ЯцICPБИ14008430КХ-1 ЯцЙЋЭјАВБИ 43070302000280КХ

- All Rights Reserved

- БОеОЮЊЗЧгЏРћЭјеОЃЌВЛНгЪмШЮКЮЙуИцЁЃБОеОЫљгаШэМўЃЌЖМгЩЭјгб

- ЩЯДЋЃЌШчгаЧжЗИФуЕФАцШЈЃЌЧыЗЂгЪМўИјxiayx666@163.com

- ЕжжЦВЛСМЩЋЧщЁЂЗДЖЏЁЂБЉСІгЮЯЗЁЃзЂвтздЮвБЃЛЄЃЌНїЗРЪмЦЩЯЕБЁЃ

- ЪЪЖШгЮЯЗвцФдЃЌГСУдгЮЯЗЩЫЩэЁЃКЯРэАВХХЪБМфЃЌЯэЪмНЁПЕЩњЛюЁЃ