ASPLOS'26丨晶圆级芯片和存算一体结合:中科院提出15万tokens/s晶圆级芯片方案

来源:互联网 2026-04-21 13:00:32Ouroboros:大模型推理与晶圆级存算一体的技术突破 当前,大模型发展呈现出显著的“军备竞赛”态势,模型参数规模从千亿级向万亿级迈进,对底层计算硬件提出了前所未有的严苛要求。在这一进程中,一个关键瓶颈日益凸显:数据搬运带来的效率损耗。 在传统计算架构中,模型推理过程往往需要在DRAM、SRAM与

Ouroboros:大模型推理与晶圆级存算一体的技术突破

当前,大模型发展呈现出显著的“军备竞赛”态势,模型参数规模从千亿级向万亿级迈进,对底层计算硬件提出了前所未有的严苛要求。在这一进程中,一个关键瓶颈日益凸显:数据搬运带来的效率损耗。

在传统计算架构中,模型推理过程往往需要在DRAM、SRAM与计算单元之间频繁搬运数据。这种访存操作不仅导致高延迟,更消耗了大量本可用于计算的能量。研究表明,数据搬运所耗费的时间远超实际计算时间,造成了巨大的资源浪费。

长期稳定更新的攒劲资源: >>>点此立即查看<<<

如何从根本上解决这一问题?答案是彻底消除数据搬运。目前,存算一体与晶圆级集成是两条备受关注的核心技术路径。

存算一体技术旨在将存储与计算功能融合在同一芯片内,实现数据的原地处理,避免远距离搬运。晶圆级集成则更为宏大,它直接在整片硅晶圆上构建超大规模系统,通过超高带宽互连,形成晶圆级的统一内存与计算资源池。

近期,中国科学院计算技术研究所的研究团队在该领域取得了突破性进展。其研究成果——Ouroboros,发表于体系结构领域顶级会议第31届ACM编程语言与操作系统架构支持国际会议(ASPLOS)。

Ouroboros是一款完全基于SRAM存算单元构建的晶圆级芯片。其核心理念是让数据“就地存储”,计算“原地执行”。在该芯片上,模型推理所需的全部数据,包括权重、KV Cache以及激活值,均存储在片上SRAM中,无需从外部DRAM搬运。所有计算均在数据存储位置完成,真正实现了“数据不移动,计算在本地”的存算一体范式。

三层架构设计:从晶圆到核心的精密布局

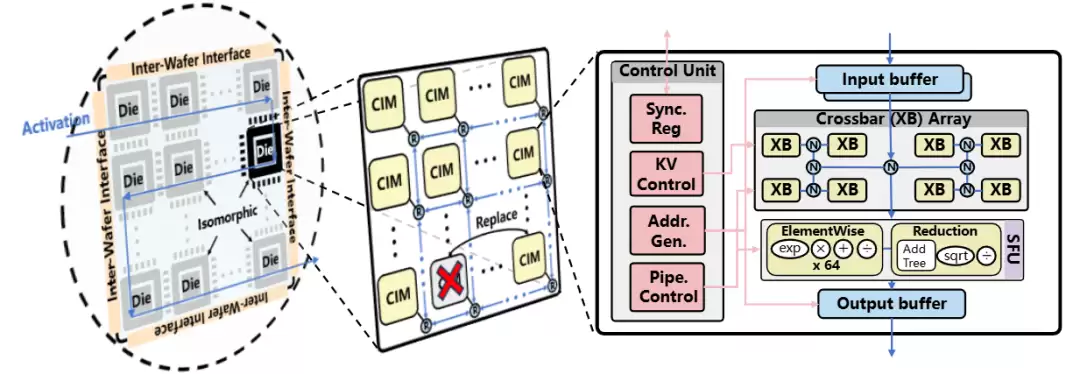

为实现这一目标,Ouroboros采用了精密的层次化设计,自上而下分为三层:

1. 晶圆级集成

顶层为巨型单晶圆,集成了高达54GB的SRAM。这片SRAM足以完整存储模型的权重、激活值与KV Cache,从而彻底消除了DRAM访问开销。整片晶圆由多个相同尺寸的小芯片通过先进缝合技术无缝拼接而成,形成一个统一调度、协同工作的巨型计算平面。

2. 芯片级组织

每个芯粒内部由上百个存算核心构成网格网络,核心间通过高带宽链路紧密互联。设计团队将芯粒面积推向光刻工艺极限,以最大化SRAM容量。同时,为确保大规模芯片的可靠性,引入了核心级容错机制。

3. 存算核心微架构

每个核心内部包含输入输出缓存、存算阵列、专用函数单元及控制单元。缓存容量经过精心设计,可容纳典型大模型的token数据,显著减少核心间数据传输。存算阵列通过优化的片上网络互联,专用函数单元以匹配的并行度高效执行softmax等关键操作,控制单元则负责协调核心间与核心内的流水线同步。

面临挑战:理想架构的现实考验

尽管Ouroboros构建了强大的晶圆级计算平面,但在运行大模型时,仍面临几个关键挑战:

第一,SRAM容量限制

虽然晶圆集成了海量SRAM,但受限于SRAM的物理密度,片上存储容量在面对持续增长的模型规模时,仍显不足。如何在有限空间内容纳日益庞大的权重和状态,是一个持续存在的难题。

第二,巨型阵列调度难题

当成百上千的计算单元铺满整片晶圆,如何高效地将复杂大模型“拆解”并精准映射到这个分布式阵列上,成为一个复杂的系统工程。存储布局、数据流调度、任务分配等均需要全新的设计思路。

第三,计算与存储的协同优化

在存算一体架构中,计算与存储高度绑定——计算发生在数据存放位置,存储布局直接制约计算效率。因此,必须对两者进行协同设计与优化,以最大化整体性能,这增加了系统设计的复杂度。

软硬协同:释放晶圆潜力的关键

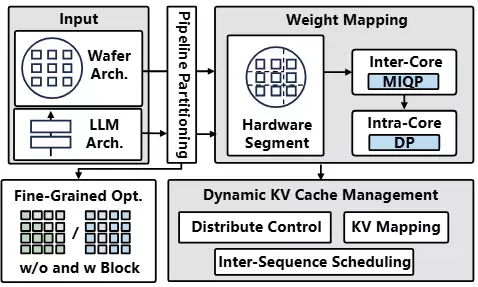

为充分释放晶圆计算潜力,研究团队开发了一套端到端的大模型推理框架。该框架从模型整体的流水线切分开始,便进行针对性精细化调整,目标是实现每一份存算资源的充分利用。

团队设计了创新的权重映射策略,不仅考虑硬件资源分配,还引入分层映射方法,旨在最大限度减少不必要的数据传输。针对大模型推理中至关重要的KV Cache,框架采用了分布式动态KV缓存管理方案及对应的硬件支持,将片上缓存的空间利用率提升至新高度。

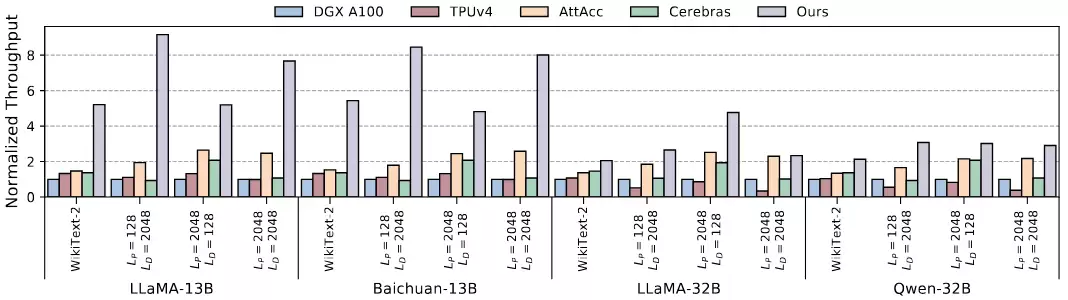

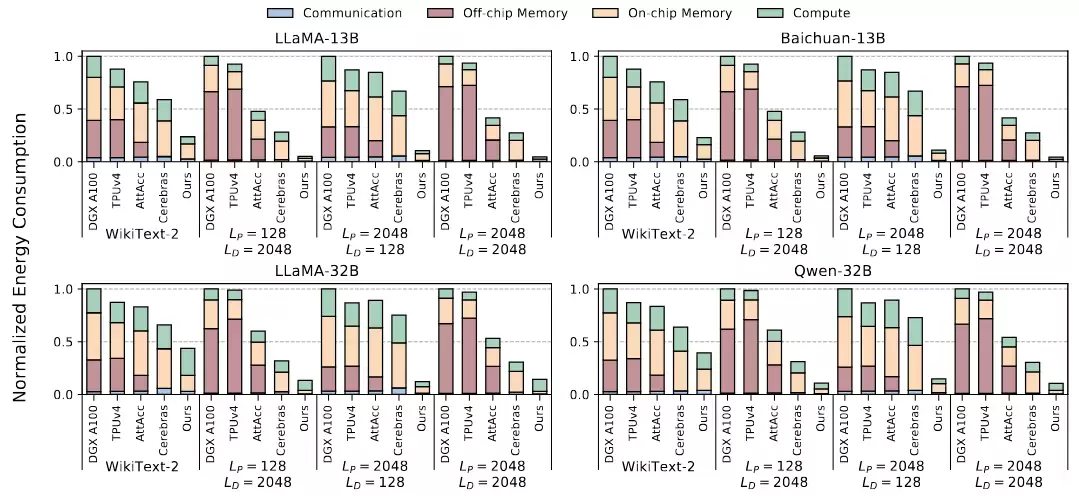

性能表现:数据验证的飞跃

通过从芯片到系统的协同设计,Ouroboros成功实现了“原地计算”理念,并在性能与能效上取得显著突破。实验数据提供了有力证明:

与现有顶尖系统相比,Ouroboros的平均吞吐量提升至4.1倍,平均能效提升至4.2倍。

在13B参数规模模型上,其表现尤为突出:吞吐量最高可达9.1倍,能效比提升至惊人的17倍。

具体而言,采用单晶圆推理Llama 13B模型、在WikiText2数据集上进行测试时,系统吞吐量可稳定达到 15万tokens/s。这一结果进一步验证了Ouroboros在真实大模型负载下的卓越性能。

上述数据不仅证实了其在性能与能效上的双重突破,更为“存算一体+晶圆级集成”这一前沿技术路线的可行性提供了有力支撑。这项研究标志着在消除数据搬运、构建下一代高效大模型推理系统的道路上,迈出了坚实的一步。

论文链接:https://dl.acm.org/doi/10.1145/3779212.3790197

作者介绍:本文作者来自中国科学院计算技术研究所智能计算机研究中心和泛在计算系统研究中心物端计算系统实验室,团队长期致力于芯粒集成芯片研究。本文的共同第一作者是刘艺圻和潘煜东,均为计算技术研究所在读博士生。指导老师为中科院计算所王颖研究员、韩银和研究员、王梦迪特别研究助理。

侠游戏发布此文仅为了传递信息,不代表侠游戏网站认同其观点或证实其描述