ФкДцЬѕШчКЮДцДЂЪ§ОнППЕФЪЧЪВУДВФСЯЃП

РДдДЃКЛЅСЊЭј 2026-05-04 07:29:08ФкДцЬѕШчКЮДцДЂЪ§ОнЃПНвУиDRAMаОЦЌЕФ1T1CНсЙЙ ФкДцЬѕДцДЂЪ§ОнвРРЕгкЦфФкВПЕФDRAMаОЦЌЃЌИУаОЦЌЕФКЫаФДцДЂЕЅдЊгЩвЛИіОЇЬхЙмКЭвЛИіЮЂаЁЕчШнЙЙГЩЃЌМДОЕфЕФ1T1CНсЙЙЁЃЕчШнЭЈЙ§ГфЕчКЭЗХЕчСНжжзДЬЌЃЌЗжБ№ДњБэЖўНјжЦЕФЁА1ЁБКЭЁА0ЁБЃЌЖјХдБпЕФОЇЬхЙмдђЯёПЊЙивЛбљЃЌПижЦзХЖдИУЕчШнЕФЖСШЁгыаДШыВйзїЁЃетжжЧЩУюЕФЩш

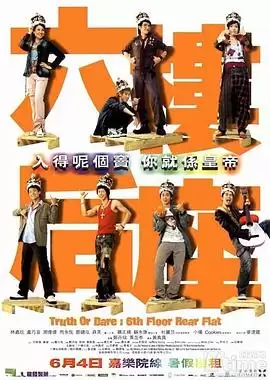

ФкДцЬѕШчКЮДцДЂЪ§ОнЃПНвУиDRAMаОЦЌЕФ1T1CНсЙЙ

ФкДцЬѕДцДЂЪ§ОнвРРЕгкЦфФкВПЕФDRAMаОЦЌЃЌИУаОЦЌЕФКЫаФДцДЂЕЅдЊгЩвЛИіОЇЬхЙмКЭвЛИіЮЂаЁЕчШнЙЙГЩЃЌМДОЕфЕФ1T1CНсЙЙЁЃЕчШнЭЈЙ§ГфЕчКЭЗХЕчСНжжзДЬЌЃЌЗжБ№ДњБэЖўНјжЦЕФЁА1ЁБКЭЁА0ЁБЃЌЖјХдБпЕФОЇЬхЙмдђЯёПЊЙивЛбљЃЌПижЦзХЖдИУЕчШнЕФЖСШЁгыаДШыВйзїЁЃетжжЧЩУюЕФЩшМЦЪЕЯжСЫЕЅЮЛУцЛ§ФкМЋИпЕФдЊМўУмЖШЃЌЪЙЕУЕЅИљЯжДњDDR5ФкДцЬѕФмЙЛМЏГЩИпДя64GBЩѕжСИќДѓЕФШнСПЁЃЫцзХCMOSжЦдьЙЄвеЕФГЩЪьЃЌетаЉЕчШнЕФГпДчвбБЛбЙЫѕжСФЩУзМЖБ№ЁЃШЛЖјЃЌЕчШнЙЬгаЕФЕчКЩаЙТЉЬиадЃЌОіЖЈСЫЦфжаДцДЂЕФЪ§ОнБиаыЖЈЦкЫЂаТЃЈЕфаЭжмЦкЮЊУП64КСУывЛДЮЃЉЃЌетвВе§ЪЧЁАЖЏЬЌЫцЛњДцШЁДцДЂЦїЃЈDRAMЃЉЁБжаЁАЖЏЬЌЁБвЛДЪЕФгЩРДЁЃЫќВЛвРРЕгкДХадЁЂЙтбЇЛђЯрБфЕШЛњжЦЃЌДПДтвдЕчКЩЕФЫВЪБДцдкзїЮЊаХЯЂдиЬхЃЌдкЭЈЕчзДЬЌЯТФмЪЕЯжФЩУыМЖЕФМЋЫйЫцЛњЗУЮЪЃЌетЙЙГЩСЫCPUИпаЇЕїЖШКЃСПСйЪБЪ§ОнЕФММЪѕЛљЪЏЁЃ

вЛЁЂЛљЪЏЃКИпДПЖШЕЅОЇЙшгыФЩУзМЖЕчШнЙЄве

ЯжДњФкДцЬѕЫљЪЙгУЕФDRAMПХСЃЃЌжЦдьЪМгкДПЖШДяЕНЁАОХИіОХЁБЃЈ99.9999999%ЃЉвдЩЯЕФЕЅОЇЙшОЇдВЁЃЭЈЙ§ЙтПЬЁЂРызгзЂШыЁЂЛЏбЇЦјЯрГСЛ§ЕШвЛЯЕСаМЋЦфОЋУмЕФАыЕМЬхжЦдьВНжшЃЌВХФмдкЙшЦЌЩЯПЬЛГіЪ§вдАйвкМЦЕФ1T1CДцДЂЕЅдЊЁЃЦфжаЕФЕчШнНсЙЙгШЮЊЙиМќЃЌЫќВЂЗЧДЋЭГЕФЦНааАхН№ЪєЕчШнЃЌЖјЪЧВЩгУСЫЁАЖбЕўЪНЁБЛђЁАЙЕВлЪНЁБЕШЩюбЧЮЂУзШ§ЮЌЩшМЦЁЊЁЊЧАепЪЧдкЙшЦЌБэУцДЙжБЖбЕўЖрВуОјдЕВФСЯгыЕМЬхЃЌКѓепдђЪЧдкЙшЛљЕзФкВПЪДПЬГіЩюЙЕВЂНјааЬюГфЁЃетаЉЯШНјНсЙЙНЋУПИіЕчШнЕФеМЕиУцЛ§ЫѕаЁжС0.01ЦНЗНЮЂУзвдФкЃЌЭЌЪБШдФмБЃГждМ20ЗЩЗЈРЕФЕчКЩДцДЂШнСПЁЃетвтЮЖзХЃЌдкDDR5ФкДцГЃМћЕФ1.1ЗќЙЄзїЕчбЙЯТЃЌЕЅИіЕчШнжЛашГфШыдМСНЭђИіЕчзгЃЌОЭФмПЩППЕиДњБэЁА1ЁБЛђЁА0ЁБЕФТпМзДЬЌЁЃ

ГЄЦкЮШЖЈИќаТЕФдмОЂзЪдДЃК >>>ЕуДЫСЂМДВщПД<<<

ЖўЁЂЮЌГжЃКФкДцПижЦЦїЕФжЧФмЫЂаТЙмРэ

ОЁЙмЕчШнТЉЕчЪЧЮяРэВуУцЕФЙЬгаЬєеНЃЌЕЋЪ§ОнЕФЮЌГждЖЗЧБЛЖЏЕШД§ЁЃЦфБГКѓЪЧвЛЬзгЩCPUФкМЏГЩЕФФкДцПижЦЦїжїЕМЕФЁЂИпЖШОЋУмЕФжїЖЏЙмРэЯЕЭГЁЃИУПижЦЦїбЯИёзёбJEDECБъзМЃЌНЋФкДцЬѕЕФТпМПеМфЛЎЗжЮЊЖрИіДцДЂЬхЃЈBankЃЉзщЃЌУПИіДцДЂЬхФкгжЪЧааСаНЛДэЕФеѓСаНсЙЙЁЃЕБЯЕЭГЯрЖдПеЯаЪБЃЌПижЦЦїЛсЦєЖЏЁАздЫЂаТЁБФЃЪНЃЌвд64КСУыЮЊжмЦкЃЌЯЕЭГЕиБщРњЫљгаааЃЌЖдЦфжаЕчШнЕФЕчКЩНјааВЙГфЁЃдкЖСаДВйзїЦЕЗБЪБЃЌдђЛсЧаЛЛЕНИќИпаЇЕФЁАздЖЏЫЂаТЁБФЃЪНЃЌЧЩУюЕиРћгУаабЁЭЈВйзїЕФМфЯЖВхШыЫЂаТЖЏзїЃЌећИіЙ§ГЬЖдCPUКЭЯЕЭГадФмЕФгАЯьЮЂКѕЦфЮЂЁЃЪЕМЪВтЪдБэУїЃЌжїСїDDR5ФкДцдк85ЁцЕФИпЮТЛЗОГЯТЃЌЦфЫЂаТжмЦкЕФЮѓВюШдФмПижЦдкЁР2%вдФкЃЌГфЗжБЃеЯСЫЪ§ОнЕФГжОУадгыПЩППадЁЃ

Ш§ЁЂЬиадЃКЖЯЕчМДЪЇЕФЮяРэБОжЪ

DRAMЕФетжжДцДЂЬиадЃЌгывРППИЁеЄОЇЬхЙмГЄЦкЗ§ЛёЕчзгЕФNANDЩСДцгаИљБОадВЛЭЌЁЃDRAMЕФЕчШнБОЩэВЛОпБИГЄЦкЫјзЁЕчКЩЕФФмСІЁЃвЛЕЉЭтВПЕчдДЧаЖЯЃЌЕчШнСНЖЫЕФЕчбЙБуЛсвђФкВПТЉЕчЖјбИЫйЫЅМѕЃЌЦфЕфаЭЕФЗХЕчЪБМфГЃЪ§НіЮЊЪ§ЪЎКСУыЁЃгаЕкШ§ЗНЪЕбщЪвЭЈЙ§ЪОВЈЦїЙлВтDDR4ПХСЃЕФЖЯЕчЙ§ГЬЗЂЯжЃЌЕчШнЕчбЙдк32КСУыФкБувбЕјТфжСЮоЗЈБЛЪЖБ№ЕчТЗХаБ№ЕФуажЕвдЯТЁЃвђДЫЃЌЫљгаЛљгкDRAMЕФФкДцЖМНіФмзїЮЊСйЪБЃЈвзЪЇадЃЉДцДЂЩшБИЃЌетжжЁАЖЯЕчМДЪЇЁБЕФЬиадЪЧгЩЦфЛљДЁВФСЯЮяРэКЭЕчТЗдРэОіЖЈЕФгВаддМЪјЃЌЖјЗЧЙЄГЬЩшМЦЩЯЕФЭзаЁЃ

змНсРДЫЕЃЌФкДцЬѕЕФЪ§ОнДцДЂФмСІЃЌЪЧЙшАыЕМЬхВФСЯЕФЕчбЇЬиадЁЂФЩУзГпЖШЕФОЋУмжЦдьЙЄвегыЪЕЪБжЧФмПижЦЫуЗЈШ§епЩюЖШаЭЌЕФГЩЙћЁЃ

ЯРгЮЯЗЗЂВМДЫЮФНіЮЊСЫДЋЕнаХЯЂЃЌВЛДњБэЯРгЮЯЗЭјеОШЯЭЌЦфЙлЕуЛђжЄЪЕЦфУшЪі

ЯрЙиЙЅТд

ИќЖрЭЌРрИќаТ

ИќЖрШШгЮЭЦМі

ИќЖр-

- КНЬьЛ№М§ФЃФтЦї

- Android/ | ФЃФтбјГЩ

- 2026-04-07

-

- УќдЫЦяЪПЭХ

- Android/ | НЧЩЋАчбн

- 2026-03-30

-

-

-

-

-

- зЙаЧДѓТН ТђЖЯАц

- Android/ | НЧЩЋАчбн

- 2026-03-30

-

- ЯцICPБИ14008430КХ-1 ЯцЙЋЭјАВБИ 43070302000280КХ

- All Rights Reserved

- БОеОЮЊЗЧгЏРћЭјеОЃЌВЛНгЪмШЮКЮЙуИцЁЃБОеОЫљгаШэМўЃЌЖМгЩЭјгб

- ЩЯДЋЃЌШчгаЧжЗИФуЕФАцШЈЃЌЧыЗЂгЪМўИјxiayx666@163.com

- ЕжжЦВЛСМЩЋЧщЁЂЗДЖЏЁЂБЉСІгЮЯЗЁЃзЂвтздЮвБЃЛЄЃЌНїЗРЪмЦЩЯЕБЁЃ

- ЪЪЖШгЮЯЗвцФдЃЌГСУдгЮЯЗЩЫЩэЁЃКЯРэАВХХЪБМфЃЌЯэЪмНЁПЕЩњЛюЁЃ